# 大規模システム開発を可能にする ハイブリッド仮想プロトタイプ技術

Hybrid Virtual Prototype Technology for Large-Scale System Development

河 邊 恭**\*** Takashi KAWABE 澤 柳 一 美**\*\*** Kazumi SAWAYANAGI

## 要旨

コニカミノルタでは、複合機をはじめとする様々なシステム製品を開発している。そのシステム製品を構成するハードウェアとソフトウェアは開発大規模化とシステム複雑化が開発課題である。システム複雑化によりハードウェアとソフトウェアの機能連携は複雑化が進み、ハードウェア/ソフトウェア協調検証の重要性は高まってきている。

我々は以前から、ロジックシミュレーション環境を使用して、LSI (large-scale integration) 完成前のハードウェアとソフトウェアの協調検証を実施してきたが、開発規模の増大によるシミュレーション速度の低下が課題となってきていた。

そこで我々は、ハードウェア/ソフトウェア協調シミュレーションを高速化し、システム製品開発の早期化を可能にする技術を開発した。それはロジックエミュレーターを活用したハイブリッド仮想プロトタイプ環境と呼ばれるものである。

近年注目されているESL (electronic system level) 技術による純粋な仮想プロトタイプ環境は、シミュレーションは高速だが、ハードウェアモデリングの開発規模という課題があった。我々はその課題を解決するため、仮想プロトタイプによるCPUなどの標準パーツのシミュレーション高速化技術と、ロジックエミュレーターによるカスタムハードウェアパーツのシミュレーション高速化技術、この両技術を組み合わせたハイブリッド仮想プロトタイプ環境を開発した。

その結果、ハードウェア/ソフトウェアの協調シミュレーションは、従来のロジックシミュレーター環境を使用したものより1260倍の高速化を達成し、さらに複数ソフトウェアコンポーネントと複数ハードウェアモジュールを組み合わせた大規模システム検証も可能となった。

この技術を用いることで、ハードウェア/ソフトウェア協調検証が現実的な開発期間内で可能となり、製品開発の早期化と品質確保に寄与することが出来た。

### **Abstract**

Konica Minolta develops and produces a variety of system products such as multi-functional peripherals (MFPs), printers and healthcare apparatuses. Developing the hardware (HW) and software (SW) that constitute these system products is constantly challenged by the products' increasing scale and complexity. On such a scale and with such complexity, achieving functional HW/SW cooperation makes HW/SW co-verification of paramount importance.

When we used a logic simulation environment to co-verify HW/SW prior to the fabrication of LSI (large-scale integration), simulation speed dropped because of the scale and complexity of the LSI. So, to speed the development of system products, we turned to HW/SW co-simulation via a hybrid virtual prototype environment utilizing a logic emulator

In a conventional non-hybrid virtual prototype environment based on ESL (electronic system level) technology, simulation is very fast, but the large-scale HW modeling involved is a bottleneck. In response, we adopted a virtual prototype to speed up the simulation of vendor-available parts such as CPUs, a logic emulator to speed up the simulation of custom HW parts, and a hybrid virtual prototype environment that combines the two.

The result was a HW/SW co-simulation 1,260 times faster than obtained with a conventional logic simulator environment: one minute versus 21 hours. Further, large-system verification combining multiple HW components and multiple HW modules was now possible. Because of this extremely rapid HW/SW co-simulation, HW/SW hybrid co-verification shortened development time down to a practical duration, thus greatly facilitating product development and quality assurance.

<sup>\*</sup>開発統括本部 システム技術開発センター アーキテクチャ開発室

<sup>\*\*</sup>開発本部 電子技術ユニット開発センター コントローラPF開発部

## 1 はじめに

複合機,プリンター,印刷用機器,ヘルスケア用機器,産業用・医用計測機器などのシステム製品は,様々なお客様の要望に対応するために高機能化および多機能化が進められている。これは半導体技術等の各種技術進化を取り入れることで実現することが可能になってきているが,それにともないハードウェアとソフトウェアの開発規模は年々増加している。しかし一方で市場ニーズにタイムリーに対応することが求められており,製品開発期間の短縮、開発効率化は重要な課題である。

特にハードウェアとソフトウェアを結合したシステム テスト (ハードウェア/ソフトウェア協調検証) は、シ ステム規模増大によるシミュレーション速度低下の影響 が大きく、システム開発における重要課題となっている。 従来、ハードウェア/ソフトウェア協調検証はロジッ クシミュレーターを使用することが一般的であったが、 シミュレーション連度が低速であるという課題があるた

クシミュレーターを使用することが一般的であったが シミュレーション速度が低速であるという課題があるため,近年はESL技術をベースとした仮想プロトタイプ技 術に注目が集まっている。

我々も以前から仮想プロトタイプ技術の研究をしてきたが、シミュレーション速度が高速という特長はあるものの、ハードウェアのモデリング規模の問題があり、実用化に課題があった。その課題を解決すべく、ロジックエミュレーターを活用したハイブリッド仮想プロトタイプ環境を開発した。本環境を使用することで、モデリング規模の問題を解決し、かつ従来のロジックシミュレーター環境と比較して1000倍以上の高速化を実現した。今回は、そのハイブリッド仮想プロトタイプ技術の特徴と成果について説明する。

#### 2 システム開発の課題

## 2.1 ハードウェア/ソフトウェア協調検証の必要性

システム製品は、ハードウェアとソフトウェアが結合 した機能による協調動作で実現されているため、ハード ウェアとソフトウェアの協調検証が必須である。

ハードウェアの主要パーツであるLSIは、RTL(register transfer level) による設計後に、半導体製造プロセス (論理合成、レイアウト、マスク製作、ウエハー製造、アセンブリ、テスト)として数カ月から半年を必要とする。

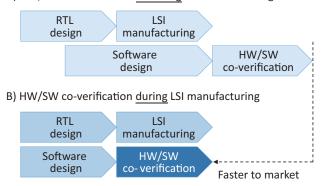

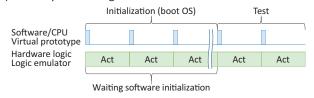

LSI製造後にハードウェア/ソフトウェア協調検証を 行うのでは開発期間の長期間化は避けられないため、 我々は以前からRTL設計データを使用した早期ハード ウェア/ソフトウェア協調検証を実施してきた (Fig. 1)。

## 2.2 ハードウェア/ソフトウェア協調検証の課題

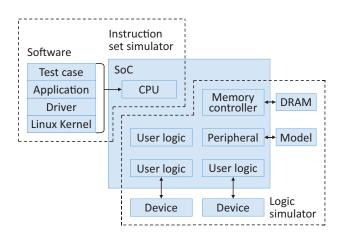

従来のハードウェア/ソフトウェア協調検証は、CPU をモデリングした ISS (instruction set simulator) を使用してソフトウェアをシミュレートし、一方でハードウェアはRTLをロジックシミュレーターでシミュレート

し, その2つのシミュレーターを連携動作させ, 協調シミュレーションを実現してきた (Fig. 2)。

しかし本手法は、低速なシミュレーターでハードウェアを高精度にシミュレートするために、シミュレーション速度が非常に遅く、開発期間と開発費に制約のある中、以下の課題があった。

- 1.検証項目を制限しなければならない

- 2. 高価なシミュレーターを多く必要とする

- 3. 長期間の検証期間を必要とする

特に検証項目を制限しなければならないという課題は、 シミュレーションで不具合を検出することが出来ずに製 品開発の後工程に不具合を流出させてしまうことにつな がり、検証品質に課題があった。

#### A) HW/SW co-verification following LSI manufacturing

Fig. 1 Hardware and software development. System verification (HW/ SW co-verification) during LSI manufacturing using RTL (resister transfer level) design data enables faster time-to-market for system products.

Fig. 2 Conventional HW/SW co-verification. The CPU is simulated by an ISS (instruction set simulator) and the hardware by a logic simulator. The two simulators work together to realize co-simulation.

## 3 ESL技術

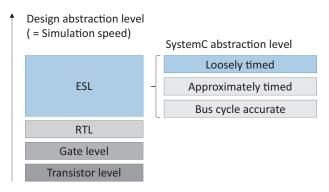

ハードウェアの高速なシミュレーションを可能にする ESLという技術概念がある。ESLはハードウェアを設計 (モデリング)する言語の抽象度を高めてシミュレーショ ン演算量を削減することで、シミュレーションの高速化を実現する技術である。以前からハードウェア設計の高抽象度化は段階的に進んできており、トランジスターレベル設計、ゲートレベル設計、RTL設計と進化してきた。ESLはRTLよりさらに設計抽象度を高めることを目標に、世界中で様々な技術開発が行われている、近年非常に注目度の高い技術である。

#### 3. 1 SystemC

高抽象度で設計できるESL言語はいくつかあるが、 我々はSystemC言語を採用している。SystemCはC++ のクラスライブラリーとして提供されており、世の中に 豊富にあるソフトウェア資産を活用できる点と、IEEE 1666-2011で標準化・規格化されていることで、SystemC 関連ツールが豊富に存在している点がメリットである。

SystemCは様々な設計抽象度で設計可能だが、我々は高い時間抽象度を持ち、ハードウェア/ソフトウェア協調検証においては十分な精度を持つLoosely Timedレベルを採用し、後述する仮想プロトタイプ開発に適用した(Fig. 3)。

Fig. 3 Abstraction level of HW design. The ESL (electronic system level) is the highest level of abstraction. On that level, we adopted the loosely timed SystemC.

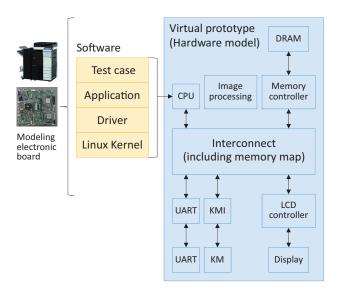

## 3.2 仮想プロトタイプ

ハードウェアをSystemCでモデリングしたものを仮想プロトタイプと呼ぶ。仮想プロトタイプでは、CPU、バス、周辺デバイスなどハードウェア/ソフトウェア協調検証に必要なハードウェアパーツ(IPコア)を全てSystemCでモデリングすることが可能である。そしてCPU上でソフトウェアを動作させることで、ハードウェア/ソフトウェア協調検証を実現することができる(Fig. 4)。各ハードウェアパーツは自社開発することも可能だが、

各ハードウェアパーツは自社開発することも可能だが、 SystemCは標準化されているため多くのツールベンダー、IPベンダーなどから入手することも可能である。 また仮想プロトタイプ用のシミュレーターやデバッガーも、いくつかのツールベンダーから入手可能である。

仮想プロトタイプは、LSI完成前にハードウェアをモデリングして、ソフトウェアを含めてシミュレーション出来ること、抽象度が高いためにシミュレーションが高速であることが特徴である。

Fig. 4 Virtual prototype environment capable of high-speed simulation. The hardware is modeled in SystemC.

## 4 ハイブリッド仮想プロトタイプ技術

## 4.1 仮想プロトタイプの課題

仮想プロトタイプはシミュレーションが高速であるという特長があるが、ユーザーロジック(カスタムパーツ)のモデリング開発という問題がある。CPUなどの標準パーツはIPベンダー等から入手可能であるが、ユーザーロジックはSystemCで自社開発する必要がある。SystemCは高抽象度のためRTLと比較すれば短期間で開発可能であるが、昨今の大規模ハードウェアのモデリングには数カ月を要する。

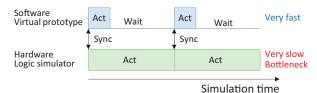

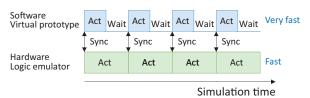

ユーザーロジックのSystemCモデリングをせずに、RTLでロジックシミュレーターに搭載すれば、モデリング開発の問題は解消する。しかしロジックシミュレーターは非常に低速なためにシミュレーション速度のボトルネックとなり、仮想プロトタイプの高速シミュレーションを生かすことが出来ない (Fig. 5)。

A) Logic simulator and virtual prototype environment: very slow

B) Logic emulator and virtual prototype environment: fast

Fig. 5 Simulation speeds. The logic simulator is very slow since the virtual prototype must repeatedly wait for synchronization. But the high speed of the logic emulator and hybrid virtual prototype makes for an extremely short wait time.

#### 4.2 高速ハイブリッド仮想プロトタイプ

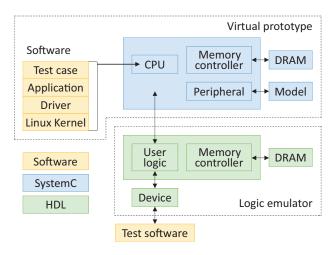

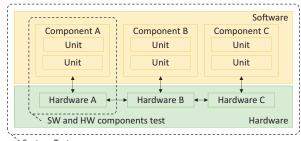

ロジックシミュレーターの低速シミュレーションを解決するため、ユーザーロジック(カスタムパーツ)のみをRTLでロジックエミュレーターに搭載するハイブリッド仮想プロトタイプシミュレーション環境を開発した(Fig. 6)。

Fig. 6 Hybrid virtual prototype environment. Vendor-available parts such as CPUs are mounted on the virtual prototype, while user logics (custom parts) are mounted on the logic emulator.

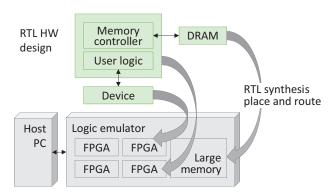

ハイブリッド仮想プロトタイプの高速シミュレーションを実現するロジックエミュレーターは,RTLを論理合成し,FPGA (field-programmable gate array) にハードウェア搭載することで,ハードウェアを高速にシミュレーションする技術である (Fig. 7)。

Fig. 7 Process and structure of the logic emulator. User logics are synthesized from the RTL (resister transfer level) and from placement and routing. They are mounted on the FPGA (field-programmable gate array) of the logic emulator.

ハードウェア規模にもよるが、ロジックシミュレーターと比較し、1000倍前後のシミュレーション高速化が可能である。

仮想プロトタイプとロジックエミュレーターを連携させるハイブリッド仮想プロトタイプにより、仮想プロトタイプの高速シミュレーションという特長を生かし、かつ仮想プロトタイプ環境の短期間開発が可能となった(Table 1)。

Table 1 Co-simulation methods. Non-hybrid virtual prototypes are fastest, but require large-scale modeling development. In contrast, virtual prototypes on a logic emulator are fast, and modeling development is small-scale.

| Method                                 | Simulation speed | Modeling development scale |

|----------------------------------------|------------------|----------------------------|

| Virtual prototype                      | Very fast        | Large                      |

| Virtual prototype<br>+ logic emulator  | Fast             | Small                      |

| Virtual prototype<br>+ logic simulator | Very slow        | Small                      |

| Logic simulator                        | Very slow        | Small                      |

#### 4.3 初期化プロセスの高速化技術

ハードウェア/ソフトウェア協調検証では、OSブートなどのシステム初期化プロセスは、検証対象外ではあるが、テストケース実行前に必要である。初期化プロセスの高速化は、検証のTAT(turn around time)改善に有効であるため、高速化の技術検討を行った。

初期化プロセスは、仮想プロトタイプに搭載したCPU/ソフトウェアとハードウェアエミュレーターに搭載したユーザーロジック等は連携動作しないという特徴があるため、仮想プロトタイプとハードウェアエミュレーターの同期頻度を低くすることができるという点に着目した。我々は、初期化プロセス実行時のみ仮想プロトタイプとハードウェアエミュレーターの同期頻度を低く制御し、ソフトウェア処理を高速に実行することで初期化プロセスの高速化/初期化時間の短縮を実現した(Fig. 8)。

## A) Actual system timing

## B) Fast initialization timing

Fig. 8 Fast initialization. Controlling the synchronous frequency of the virtual prototype and logic emulator during initialization speeds up initialization by reducing wait time.

## 5 結果と成果

## 5.1 シミュレーション速度

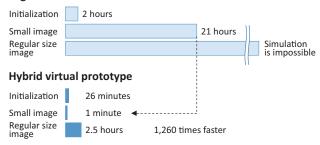

我々が開発したシステムにおける、ハイブリッド仮想プロトタイプ環境と従来のロジックシミュレーター環境のシミュレーション時間を比較した結果を示す (Fig. 9)。初期化時間は4.6倍、初期化を除くテストケースのシミュレーション時間は1260倍の高速化を達成した。従来は小サイズテストでも23時間を必要とし、通常サイズのテストは時間的に実施不可能であった。しかしハイブリッ

ド仮想プロトタイプ環境は通常サイズテストでも3時間でシミュレーションが可能になり、実用的な時間でテストが可能になった。この結果、小サイズテストでは発見不可能な不具合の検出が可能になり、早期にソフトウェアならびにシステムの品質向上が可能になった。

#### Logic simulator

Fig. 9 Simulation times of a logic simulator and a hybrid virtual prototype on a logic emulator. The hybrid virtual prototype is 1,260 times faster than the logic simulator.

#### 5.2 システム検証

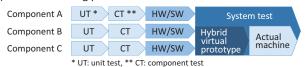

大規模なソフトウェアでは、ユニットテスト、結合テスト、システムテストと、段階的にテストを実施していく。しかし複数のソフトウェアコンポーネントとハードウェアを結合するシステムテストは、シミュレーション時間の問題で従来はLSI完成後の実機テストに頼らざるを得なかった。しかしハイブリッド仮想プロトタイプ環境ではシミュレーションが非常に高速なため、シミュレーションによるLSI完成前のシステムテストが実現可能になった(Fig. 10)。

### A) Test target region

` System Test

## B) Software testing process

Fig. 10 System test: co-verification of software and hardware components. With the hybrid virtual prototype, system testing can be done prior to fabricating an actual physical prototype.

従来はハードウェアの実物が完成後に実機を使用したシステムテストを実施していたため、複数コンポーネント間の仕様不整合による不具合が実機テストで発覚していた。また実機テスト環境はシミュレーション環境と比較して解析性に劣るため、不具合原因解析/不具合修正

に時間を要し、かつ多大なコストが必要であった。しか しハイブリッド仮想プロトタイプ環境による事前システ ムテストを実施することで、後工程の実機システムテス トへの不具合流出を削減することができ、システム製品 の品質、コスト、納期を改善することが可能になった。

### 6 まとめ

ハードウェアとソフトウェアの協調シミュレーションの高速化を目的に、ESL技術である仮想プロトタイプとハードウェアの高速シミュレーション技術であるロジックエミュレーターを連携させる、ハイブリッド仮想プロトタイプによるハードウェア/ソフトウェア協調シミュレーション環境を開発した。従来のロジックシミュレーターと比較し、1260倍のシミュレーション高速化を実現し、通常サイズのシミュレーションとシステムテストの早期化を実現した。その結果、ハードウェアとソフトウェアの早期品質確保が可能になった。

以上の技術開発により確立された技術は、システム開発の品質を高め、かつ効率化するための基盤技術として、既に社内の多くのシステム製品開発に適用している。今後は、これらの技術をより高度化/最適化し、今後も大規模化するシステム製品開発に対応していく。