# ESD対策技術の開発

**Development of ESD Simulation Technology**

浅野 斉\* 野村 毅\*\* 関 裕正\*

Hitoshi ASANO Takeshi NOMURA Hirotada SEKI

## 要旨

コニカミノルタは電子機器の誤動作を引き起こすESD (静電気放電) に対し、以下の対策技術を開発した。

従来ESDにより電子機器内に発生するESDノイズ(電気的ノイズ)を正確に測定する手段が存在しなかった為、ESD障害のメカニズム究明が進まず、ESDシミュレーション用のモデル作製も進んでいなかった。しかし近年、ESDノイズを測定可能な測定器(光プローブ:精工技研製)が開発された為、コニカミノルタは光プローブを活用したESD障害のメカニズム研究、及びESDシミュレーションモデルの作製に着手した。

本研究はMFPのESDシミュレーションモデル作製に 先立ち、MFPの構成を簡素化した実験機と実験機のESD シミュレーションモデルを作製、光プローブで測定した 実験機内のノイズ波形と、シミュレーションで演算した ESDノイズ波形とを比較検証する事で、ESDシミュレー ションモデルの有効性と精度の検証を行ったものである。

一般的にMFPのESD感受性は再現性が低く、その主要因はケーブル位置と板金間接続が不安定であることと考えられてきた。そこで実験機は構成を極力単純化。MFPの板金を一枚の金属平板に、ケーブルをFFCに、電源コードを1本の銅線に置き換える事で形状と接続の再現性を確保した。これらの構成の簡素化により、実験機内のESDノイズ波形においては光プローブの測定結果とESDシミュレーション結果の電圧がほぼ一致、製品開発に使用可能な精度を持っていることを確認できた。今後実験機で作製したシミュレーションモデルを元にMFPのシミュレーションモデルを作製し、光プローブでの測定を以って精度確認を行っていく予定である。

また、これまで提案されてこなかった、ESDノイズに対するICの感受性評価方法も併せて試行した。測定法はICのノイズ感受性試験の一つであるDPI法(IEC 62132-2)を選択、調査したICにおいてDPI法でのIC誤動作電圧とESD試験でのIC誤動作電圧が一致していることを確認した。今後各種ICの誤動作電圧を調査し、ESDノイズに対するICの感受性評価方法として活用していく予定である。

#### **Abstract**

Konica Minolta has developed a means of measuring ESD (electrostatic discharge), which causes malfunctions of electronic equipment. Conventionally, there has been no tool capable of accurately measuring ESD, thus hampering the simulation of ESD. However, we have recently developed a means of replicating MFP (multi-function peripheral) ESD employing an optical probe manufactured by Seikoh Giken. We further produced an MFP ESD simulation model for comparison.

In many cases, MFPs are detrimentally sensitive to ESD. The chief factors in this over-sensitivity appear to be the physical layout of an MFP's wiring and the electrical grounding connections of the electronics to the MFP's chassis. In designing our MFP ESD replication device, we represented an MFP chassis with a single, flat metal plate. Further, we represented the wiring of an MFP with an FFC (flexible flat cable) and represented the MFP's power supply grounding with a single copper wire. These simplifications achieved an almost perfect match between the ESD noise waveforms of our measurements and the noise waveforms of our ESD simulation results. This portends that our ESD simulation is accurate enough to be used in developing new products. In the future, we expect to construct an MFP ESD replication device more representative of actual MFPs with a correspondingly even more accurate ESD simulation model.

In addition, we conducted a sensitivity evaluation of ESD noise employing the DPI (direct power injection) method (IEC 62132-2). The logic IC (integrated circuit) malfunction voltage determined by the DPI method and the logic IC malfunction voltage returned by the MFP ESD model replication were found to be at the same level. In the future, we will investigate the malfunction voltage of various logic ICs employing our simulation as an ESD noise sensitivity evaluation method.

<sup>\*</sup>情報機器開発本部 第1エンジン制御開発部

<sup>\*\*</sup>情報機器開発本部 CAE推進部

## 1 はじめに

電子機器の誤動作を引き起こす要因の一つに、人体から電子機器へのESD (Electro Static Discharge:静電気放電)障害がある。人体が電子機器に触れる際、人体に帯電した静電気が電子機器に放電するが、その際に電子機器内に発生する電気的ノイズ(以降ESDノイズと呼称)により電子機器内のICが誤動作する障害である。

このESDに対する電子機器の感受性を定量評価するためIEC61000-4-2という国際規格が存在しており、規格に準拠したESD試験機にてESD感受性試験が行われている。しかしESD試験機の放電電圧は4kVを超える高電圧であり、更にオシロスコープを電子機器に接続するとESDノイズがオシロスコープに流入してしまうため、電子機器内のESDノイズを正確に測定する手段が存在しなかった。

これまでコニカミノルタではESD対策の設計手段として、電磁界シミュレーターによるESDシミュレーションを試行してきたが、シミュレーションで得たESDノイズレベルを実測検証する手段が存在しなかった為、ESDシミュレーションの有効性とシミュレーションモデルの精度を評価する事ができなかった。

しかし近年、ESD / イズを測定可能な測定器(光プローブ:精工技研製)が登場し、各社でその運用が始まってきた。そこで今回コニカミノルタは、MFP用のESDシミュレーションモデルの開発に着手、併せてこれまで提案されてこなかったESD / イズに対するICの感受性評価方法の開発にも着手した。

ESDシミュレーションモデルは、最終的にはMFPのモデル化を目指すが、MFPの製品構成は極めて複雑であり、シミュレーションには膨大な時間が必要となる。また機内配線等、構成上のばらつき要素も多い為、検証実験においての再現性の低下が懸念される。そこで今回はMFPを簡素化した実験機を作製し、実験機のESDシミュレーションモデルを作製して、比較検証を実施した。今後、実験機のESDシミュレーションモデルをベースに、MFPのESDシミュレーションモデルを作製していく予定である。

ICのノイズ感受性評価方法は、今回1種のICでのみ試行した。今後MFPに搭載される様々なICのESDノイズ感受性を把握する事で、シミュレーションによるMFPのESD対策設計を行っていく予定である。

## 2 ESDノイズの把握(測定とシミュレーション)

#### 2.1 ESDノイズ測定用実験機の作製

ESD障害におけるMFPの特徴として、板金筐体を有すること、板金筐体は電源コードによりアース接続されていること、ESDは板金筐体もしくは板金筐体に電気的に接続された板金に印加されること、ICを搭載した複数の回路基板が筐体板金に電気的に接続されていること、複

数の回路基板のICの信号はハーネス,ケーブル,FFC (Flexible flat cable:カード電線),等の電線で接続されていること,前述の信号を持つICにおいてESD障害が発生し易いことが上げられる。

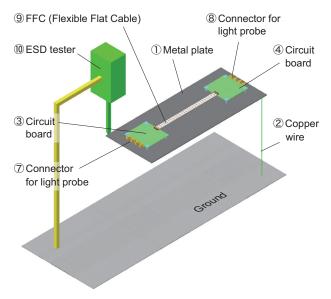

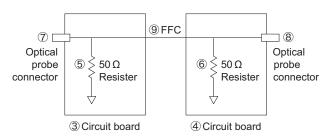

そこで実験機はFig. 1 の構成及びFig. 2 の回路図に示す、以下の構成とした。板金筐体の代わりとなる金属平板①を水平に配置、銅線②はアース線であり①から鉛直にGNDプレーン(実験室の金属床)に接続、2 枚の回路基板③④を①の上面にネジ止め接続、③④それぞれの信号線にICの代わりとなる50 Ω抵抗⑤⑥と光プローブ接続用のコネクタ⑦⑧を搭載、FFC⑨で③④の信号線同士を接続する。ESD試験機⑩で①に対して放電し、⑦⑧に光プローブを接続してESD ノイズ波形を測定する。

Fig. 1 MFP ESD replication device.

Fig. 2 Circuit diagram of the MFP ESD replication device.

To check the effect of the circuit impedance on ESD noise, measurement via our MFP ESD replication device and our MFP ESD simulation were conducted both with and without 50  $\Omega$  resistors.

一般的にMFPのESD感受性は再現性が低く、その主要因はケーブルの配置が不安定であること、および板金間の電気接続が不安定であることと考えられてきた。そこで今回の実験機はMFPの板金構成を極力単純化して金属平板①に置き換え、MFP内のケーブルをFFC⑨に置き換え、電源コードによるアースは銅線②に置き換えている。これらの構成の簡素化によりESDノイズの再現性の確保が可能となり、形状の単純化によりESDシミュレーションの高速化が可能となった。

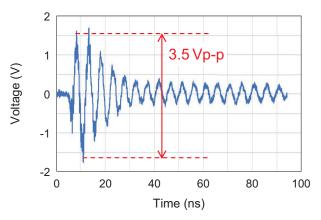

Fig. 3 は金属平板①にスリットを有するもので、スリットが無い場合に比べて構造が複雑な為、発生するESD/イズのレベルが増大する。

Fig. 3 FP ESD replication device with slit.

The slit is provided to make the device structure more complex. To check the effect of the complexity of the metal plate structure, measurement and simulation were conducted both with and without the slit.

#### 2.2 ESD シミュレーションモデルの作製

前述の実験機は金属平板①と銅線②、回路基板③④、50Ω抵抗⑤⑥、光プローブ用コネクタ⑦⑧、FFC⑨で構成される。ESDシミュレーションモデルとしてコニカミノルタは、材料と形状の明確な①~④⑨を3Dモデルとして定義し、50Ω抵抗⑤⑥は抵抗値として定義した。光プローブ用のコネクタ及びその配線は本来不要な部品である為、シミュレーションモデルから除外した。他にESD試験機のシミュレーションモデルを作製する必要もあるが、このモデルは、既に一般公開されている3Dモデルを使用□。ESD試験機から実験機に流入する電流波形がESDシミュレーションと実際の電流波形とで近似するよう、このESD試験機モデルのパラメーターを調整してESDシミュレーションモデルを作製した。

## 2.3 ESD シミュレーションモデルの精度検証

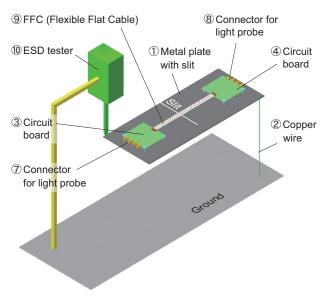

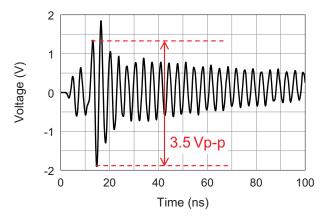

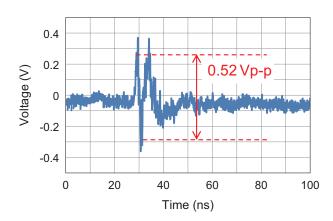

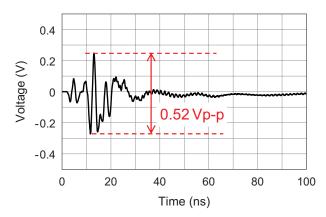

2.2のESDシミュレーションモデルの精度を検証するため、2.1の実験機で測定したESDノイズ波形とESDシミュレーションで得たESDノイズ波形の比較検証を行った。実験機(スリットあり、Fig.3)にESD 1kVを印加し、光プローブで測定したESDノイズ波形と、ESDシミュレーションで得たESDノイズ波形とをFig.4、5、6、7に示す。

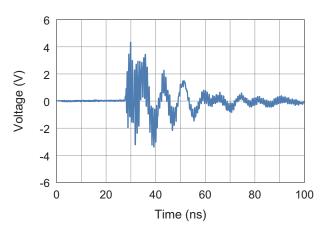

Fig. 4, 5 は回路基板④⑤の $50\Omega$ 抵抗を非搭載, Fig. 6, 7 は回路基板④⑤の $50\Omega$ 抵抗を搭載した場合の波形である。Fig. 5, 7 は ESD シミュレーションで得た ESD ノイズ波形であり、Fig. 4, 6 は光プローブで測定した ESD ノイズ波形である。

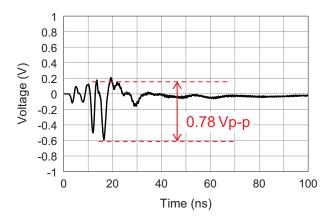

Fig. 4 ESD noise waveform, measured with optical probe, of MFP ESD replication device with slit and without  $50\,\Omega$  resistor (ESD voltage 1 kV). The connecter for the optical probe causes high frequency noise of 2 GHz on the waveform measured with our MFP ESD replication device. However, this noise can be ignored because no optical probe connecter is typically mounted on an MFP. The amplitude of the noise is about 3.5 Vp-p when high frequency noise is ignored.

Fig. 5 Simulated ESD noise waveform with slit and without 50  $\Omega$  resistor (ESD voltage 1 kV).

The amplitudes of the measurement results (Fig. 4) and the simulation results (Fig. 5) are nearly the same voltage of 3.5 Vp-p. The same measurement and simulation were conducted without a slit and with the same results: the amplitudes were virtually the same.

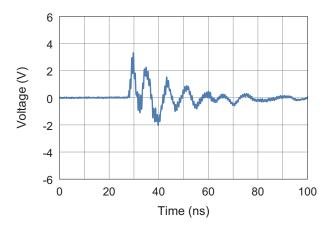

Fig. 6 ESD noise waveform measured the MFP ESD replication device, with slit and with 50  $\Omega$  resistors (ESD voltage 1 kV).

As with Fig. 4, a high frequency noise of 2 GHz is superimposed on the waveform measured with the MFP ESD replication device, but this noise can be ignored because no optical probe connecter is typically mounted on an MFP. The measured amplitude of the noise is about 0.52 Vp-p when high frequency noise is ignored.

Fig. 7 Simulated ESD noise waveform, with slit and 50  $\Omega$  resistor (ESD voltage 1 kV).

The amplitudes of the measurement results (Fig. 6) and the simulation results (Fig. 7) are both 0.52 Vp-p and almost the same. The same comparison was conducted without slits, and the same results (the amplitudes were the same) were obtained.

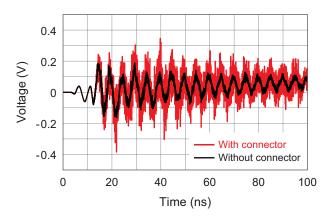

Fig. 8 Results of the simulation model with and without optical probe connectors, with ESD voltage of 1 kV and with LVDS (low voltage differential signaling) logic ICs mounted instead of 50  $\Omega$  resistors. The graph shows that the optical probe connectors increase the high frequency noise at 2 GHz.

光プローブで測定したESDノイズ波形(Fig. 4, 6)には2GHzの高周波ノイズが重畳しているのに対し、ESDシミュレーションで得たESDノイズ波形(Fig. 5, 7)には2GHzの高周波ノイズがほとんど存在しないが、その原因は光プローブ接続用のコネクタとコネクタへの信号配線によるものである。一般的にICからICへ配線された高速信号を、このように分岐すると信号の反射が発生する。今回2GHzの高周波ノイズが信号反射による共振を引き起こしており、光プローブの測定波形に重畳していた。ESDシミュレーションモデルに光プローブ用コネクタと分岐された信号を追加した場合の、シミュレーションによるESDノイズ波形をFig. 8 に示す。光プローブ用コネクタと分岐配線により、2GHzの高周波ノイズが増大している事が判る。

実際の製品が光プローブ用コネクタと分岐配線を搭載する事は無く、Fig. 4,6 に現れた2GHzノイズが製品において増大する事な無いため、無視して良いノイズであるといえる。

$2\,\mathrm{GHz}$ のノイズ成分を無視した場合, $50\,\Omega$ 抵抗非搭載時の $\mathrm{ESD}$ ノイズ電圧は図 $\mathrm{Fig.}$ 4,5 共に約 $3.5\,\mathrm{Vp-p}$ 。 $50\,\Omega$ 抵抗搭載時の $\mathrm{ESD}$ ノイズ電圧は $\mathrm{Fig.}$ 6,7 共に約 $0.52\,\mathrm{Vp-p}$ 。  $\mathrm{ESD}$ シミュレーションによる波形と光プローブで測定した $\mathrm{ESD}$ ノイズ波形は形状こそ異なるものの,そのノイズ電圧はほぼ同値である事が判る。

これらのESDシミュレーションと光プローブの波形比較検証は、金属平板にスリットを有する実験機(スリットあり、Fig. 3)によるものであるが、同様の比較検証をスリットの無い実験機(スリットなし、Fig. 1)でも実施しており、同様の結果を得ている。

以上の結果から、製品開発でESDシミュレーションを 使用するのに対し、今回作製したESDシミュレーション モデルは十分な精度を備えているものと判断する。

#### 2.4 ESDノイズの特徴と考察

これまでの結果から、IC端子に発生するESDノイズ波形は、信号の回路インピーダンスと回路間の板金構成により変動する事が判る。板金構成によりノイズレベルが変動し、回路インピーダンスにより共振周波数とノイズレベルが変化する。 $50\Omega$ 抵抗非搭載時のように回路インピーダンスが高ければ、ノイズは高レベルとなり高周波数で共振する。 $50\Omega$ 抵抗搭載時のように回路インピーダンスが低ければ、ノイズは低レベルとなり、共振はすぐに収束する。

ESDノイズを抑制する為には、基板間の板金構成を単純化し、信号の回路インピーダンスを低く抑えることが 肝要となる。

このESDノイズ波形の発生傾向は、実験機においても実際のMFPにおいても変わらないと予想しており、今後コニカミノルタのMFP開発において、以上の知見と光プローブによるESDノイズ波形測定を導入していく予定である。

## 2.5 ICのESDシミュレーションモデルの作製

これまでESDシミュレーションの有効性を把握する為,ICの代わりに $50\Omega$ 抵抗を搭載した実験機,およびそのESDシミュレーションモデルで研究を行ってきたが,製品開発で使用する為には,ICをESDシミュレーションモデルに組み込む必要がある。しかしICの内部回路は複雑かつ膨大である為,簡素な等価回路に置換える必要がある。

そこでコニカミノルタは以下の手法でICのモデル化を実施した。①動作中のIC端子の負荷インピーダンスを測定する。②負荷インピーダンスに近似する等価回路を回路シミュレーションで作製する。

この手法により、内部構造の不明なICにおいても等価 回路を導出することが可能となった。

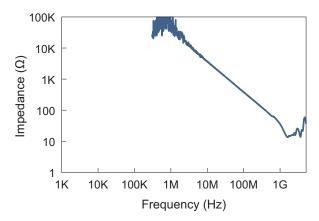

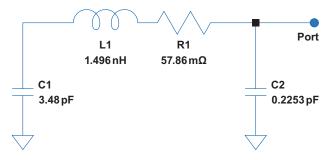

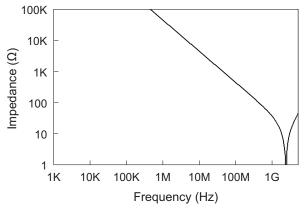

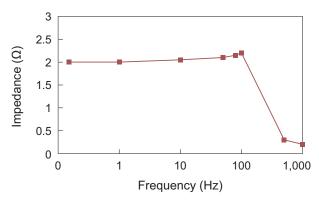

Fig. 9 に汎用ロジック IC (LVC2G07) の信号端子の負荷インピーダンス, Fig. 10 に今回導出した等価回路, Fig. 11 に等価回路の回路シミュレーションによる負荷インピーダンスを示す。

Fig. 9 Measured impedance of logic IC (LVC2G07).

Fig. 10 Circuit schematic equivalent to Fig. 9 was created using SPICE (simulation program for integrated circuits emphasis) to approximate the measured impedance of a logic IC and was used as a simulation model of the logic IC.

Fig. 11 SPICE simulation of impedance of equivalent circuit schematic of logic IC in Fig. 10.

## 2. 6 IC ESD シミュレーションモデルの精度検証

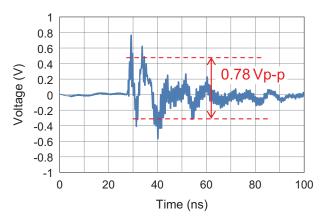

ICのESDシミュレーションモデル (等価回路, Fig. 10) の精度を検証する為,実験機 (スリットあり, Fig. 3) において50Ω抵抗の代わりに汎用ロジックIC (LVC2G07) を搭載。ICの信号端子上に発生するESDノイズ波形を,ESDシミュレーション結果と光プローブ測定結果とで比較検証した。

Fig. 12, 13 に ESD 1 kV で発生した IC 信号端子の ESD 1 / イズを示す。Fig. 12 は光プローブで測定した ESD 1 / ズ波形,Fig. 13 は ESD シミュレーションで得た ESD 1 / ズ波形であり,波形の形状は異なるものの 1 / ズ電圧は両者共に約1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1

Fig. 12 ESD noise waveform, measured with MFP ESD replication device with slit with logic ICs (ESD voltage 1 kV).

The amplitude of the noise is about 0.78 Vp-p when high frequency noise is ignored.

Fig. 13 Simulated ESD noise waveform (with slit) with logic ICs (ESD voltage 1 kV).

Measurement results (Fig. 12) and simulation results (Fig. 13) exhibit different waveforms, but the both waveforms have the same amplitude of approximately 0.78 Vp-p.

以上の比較検証は実験機 (スリットあり、Fig. 3) によるものあるが、実験機 (スリットなし、Fig. 1) においても同様の検証結果を得ている。

以上の結果から、製品開発でESDシミュレーションを 使用するのに対し、今回作製したICのESDシミュレー ションモデルは十分な精度を備えているものと判断、今 後、順次ICのモデル数を増やし、製品開発に適用してい く予定である。

## 3 ESDノイズに対するIC感受性の把握

# 3.1 ICの感受性評価方法の考案

以上の取組みにより電子機器内に発生するESDノイズの測定,及びシミュレーションが可能となったが,製品開発でESDシミュレーションを運用する為には,ICのESDノイズに対する感受性を把握する必要がある。

これまでESDノイズの波形を測定する事が出来なかった為,ICのノイズ感受性(誤動作が発生する閾値)を定量評価する手法は存在しなかったが,前述のように光プ

ローブとESDシミュレーションでESDノイズ波形を捉えることが可能となり、またESDノイズ波形は信号の回路インピーダンスに応じた特定の周波数を有するノイズである可能性が高いことが判ってきた為、コニカミノルタはESDノイズに対するICの感受性評価方法の開発に着手した。

ICのESDノイズ感受性の評価方法として、一般的なIC のノイズ感受性試験の一つであるDPI法 (IEC 62132-2)を選定した。

DPI法は動作状態のICの電源端子、信号端子に対してコンデンサカップリングによりACノイズを注入する試験方法であり、ACノイズの周波数と電力を変化させながらICの動作状態を観察して、各周波数での誤動作閾値を把握する。本来のDPI法はノイズ発生器のアンプの投入電力をモニターしながら実験するが、今回把握したいパラメーターは投入電力ではなく、IC端子の電圧である。よってコニカミノルタは信号端子に発生するノイズ電圧をモニターしながら実験を行う事にした。

MFPのESD/イズに対するICの/イズ感受性が、DPI 法での/イズ感受性と一致すれば、DPI法をESD/イズ の感受性評価方法として採用する事ができる。そこでコ ニカミノルタは、以下の検証実験を行った。

#### 3.2 ESDノイズに対するIC感受性の把握

ESDノイズに対するICのノイズ感受性を把握する為,2.1で作製した実験機を使用, $50\Omega$ 抵抗の代わりにICを搭載した。実験機に印加するESD電圧を少しずつ上げてICが誤動作する閾値を把握,ESD誤動作閾値でのESDノイズ波形を光プローブで測定し,その周波数と電圧を確認する事でICのESDノイズに対する感受性,即ちESDノイズに対する誤動作閾値電圧を把握した。

Fig. 14 は汎用ロジックIC (LVC2G07) を実験機 (スリットなし, Fig. 1) に搭載してESD試験を行った結果であり、Fig. 15 は汎用ロジックIC (LVC2G07) を実験機 (スリットあり、Fig. 3) に搭載してESD試験を行った結果である。

Fig. 14 Measured ESD noise waveform (without slit) with logic ICs at the point where ESD noise caused malfunction of logic ICs (ESD voltage 7.9 kV).

Fig. 15 Measured ESD noise (with slit) with logic ICs at the point where ESD noise caused malfunction of logic ICs (ESD voltage 3.3 kV).

Malfunctions were caused at different ESD voltages depending on the presence or absence of the slit, but the malfunction was caused by the ESD noise voltage of 2 V regardless of the presence or absence of the slit. This indicates that the threshold of ESD noise causing malfunction of logic ICs is 2V at 100 MHz.

スリットの有無で、誤動作を引き起こしたESD電圧はそれぞれ異なるが、その時のESDノイズ電圧は両者共に2Vである。この結果から汎用ロジックIC(LVC2G07)のESDノイズに対する誤動作閾値は100MHzにおいて2Vであると判断できる。

#### 3.3 DPI法に対するIC感受性の把握

Fig. 16 にDPI法による, 汎用ロジックIC (LVC2G07) のノイズ感受性 (誤動作閾値) の試験結果を示す。

100 MHz 以下の低周波数では誤動作閾値が2Vであるのに対し、300 MHz以上の周波数においてはノイズ感受性が悪化、0.2VでIC 誤動作が発生した。

Fig. 16 Noise sensitivity of logic IC (LVC2G07) measured by DPI (direct power injection).

This shows that noise sensitivity is at the threshold of logic IC malfunction at 2 V at a frequency of 100 MHz or lower, confirming that the threshold of malfunction was the same between the ESD noise measurement and DPI.

100 MHz以下の周波数においては、汎用ロジックIC (LVC2G07) は正常な応答をしているものと考える。即ちノイズ電圧がICのスレッシュホールド電圧以下ならば "L"と判断し、スレッシュホールド電圧以上ならば "H"と

判断、IC自体は正常機能しているものと考える。しかし 300 MHz以上の信号に対しては、応答速度の限界から半 導体が反応できなくなり、ICが異常動作を引き起こして いるものと想定している。

## 3.4 ESDノイズとDPI法のIC感受性の比較

以上,汎用ロジックIC (LVC2G07) の誤動作閾値は,ESDノイズにおいては2V (周波数100MHz), DPI法においても2V (100MHz) となり,一致する事が確認できた。ESDノイズに対する汎用ロジックIC (LVC2G07)の誤動作閾値は100MHz以下において2Vと判断する。

3.2に示したESD試験によりESDノイズの誤動作閾値を把握することはできるが、周波数に対するICの誤動作閾値の変化を把握する事はできない。製品構成によりESDノイズの誤動作周波数は変動する為、各周波数での誤動作閾値を3.3に示したDPI法で把握していく事が必要となる。

今回は汎用ロジックIC(LVC2G07)についての評価を行ったが、今後MFPにおいて使用される各種通信IC (LVDS, V-by-One, 等)に対しても評価していく予定である。

## 4 おわりに

以上、コニカミノルタで実施したESD対策に関わる設計プロセスの為の研究について述べた。この研究は単純な構造の実験機にて行ったが、今後、実際のMFPに研究対象を拡大、MFPのESDシミュレーションモデルを作製、検証する予定である。本研究で把握したESDノイズ波形の特徴を元に有効なESD対策手段を選定し、更に設計段階でESDシミュレーションにより最適な対策を行う事でESD対策部品費の低減、ESD対策工数の削減と開発期間の短縮も実現するよう、研究に努めていく。

#### ●引用文献

1) 静電気試験法による放電電流のFDTDシミュレーション電子情報通信学会論文誌2003/11 Vol. J86-B No. 11 藤原 修 他